- Raspberry Pi & Accessories

- Raspberry Pi Kits

- Raspberry Pi Board

- Raspberry Pi Case

- Raspberry Pi Came

- Raspberry Pi Accessories

Electronic Devices And Components

Showing 461–480 of 1018 results

- 74LS And 74HC Series IC

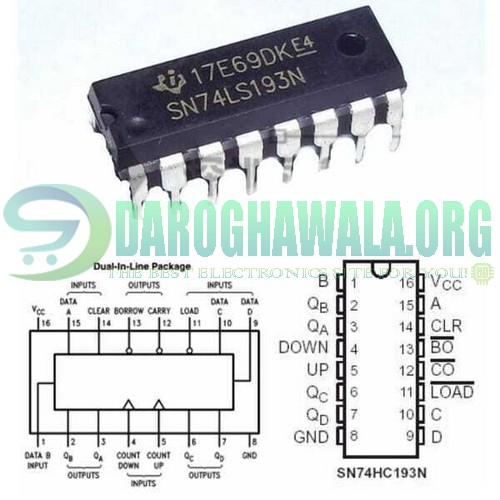

74193 Synchronous 4 Bit Binary Counter DIP IC SN74LS193N 74HC193 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74193 Synchronous 4 Bit Binary Counter DIP IC SN74LS193N 74HC193 in Pakistan

This circuit is a synchronous up/down 4-bit binary counter. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change together when so instructed by the steering logic. This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple clock) counters. The outputs of the four master-slave flip-flops are triggered by a low-to-high level transition of either count (clock) input. The direction of counting is determined by which count input is pulsed while the other count input is held high. The counter is fully programmable; that is, each output may be preset to either level by entering the desired data at the inputs while the load input is low. The output will change independently of the count pulses.

SKU: D2015 - 74LS And 74HC Series IC

74238 SN74HC238N 74HC238 74LS238 DIP 16 Pin IC in Pakistan

These are high-speed silicon-gate CMOS decoders well suited to memory address decoding or data-routing applications. Both circuits feature low power consumption usually associated with CMOS circuitry, yet have speeds comparable to low-power Schottky TTL logic. Both circuits have three binary select inputs (A0, A1, and A2). If the device is enabled, these inputs determine which one of the eight normally high outputs of the HC/HCT138 series goes low or which of the normally low outputs of the HC/HCT238 series go high. Two active low and one active high enables (E1, E2, and E3)are provided to ease the cascading of decoders. The decoder’s eight outputs can drive ten low-power Schottky TTL equivalent loads.

SKU: D2021 - 74LS And 74HC Series IC

7447 74HC47 74LS47 BCD to 7 Segment Decoder Driver DIP 16 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC7447 74HC47 74LS47 BCD to 7 Segment Decoder Driver DIP 16 in Pakistan

74LS47 accepts four lines of BCD (8421) input data, generates their complements internally and decodes the data with seven AND/OR gates having open-collector outputs to drive indicator segments directly. Each segment output is guaranteed to sink 24 mA in the ON (LOW) state and withstand 15V in the OFF (HIGH) state with a maximum leakage current of 250 µA. Auxiliary inputs provided blanking, 74LS47 BCD to 7-Segment Decoder/Driver IC.

SKU: D2008 - 74LS And 74HC Series IC

7448 BCD To 7 Segment Decoder Driver IC 74LS48 SN74LS48N 74HC48 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC7448 BCD To 7 Segment Decoder Driver IC 74LS48 SN74LS48N 74HC48 in Pakistan

The 74LS48 features active-high outputs for driving lamp buffers or common-cathode LEDs. They have full ripple-blanking input/output controls and a lamp test input. Display patterns for BCD input count above 9 are unique symbols to authenticate input conditions. Their circuits incorporate automatic leading and/or trailing-edge zero-blanking control (RBI\ and RBO\). Lamp test (LT\) of these types may be performed at any time when the BI\/RBO\ node is at a high level. They contain an overriding blanking input (BI\), which can be used to control the lamp intensity by pulsing or to inhibit the outputs. Inputs and outputs are entirely compatible for use with TTL logic outputs.

SKU: D2010 - 74LS And 74HC Series IC

7490 74LS90 IC Decade Counter in Pakistan

Each counter has a divide-by-two section and either a divide-by-five (LS90), divide-by-six (LS92) or divide-by-eight (LS93) section which are triggered by a HIGH-to-LOW transition on the clock inputs. Each section can be used separately or tied together (Q to CP) to form BCD, bi-quinary, modulo-12, or modulo-16 counters. All of the counters have a 2-input gated Master Reset (Clear), and the LS90 also has a 2-input gated Master Set (Preset 9).

SKU: D2012 - 74LS And 74HC Series IC

74hc138 IC in Pakistan

The 74HC138 is a high-speed CMOS device. The device accepts a three-bit binary weighted address on input pins A0, A1, and A2 and when enabled will produce one active low output with the remaining seven being high. There are two active LOW enable inputs E1 and E2, and one active HIGH enable input E3. The disabled device state results in all outputs being high. The enable state occurs with E1 and E2 asserted low and E3 asserted high. The multiple enable lines to allow for the parallel expansion of decoders to create 4-to-16 line versions with no additional parts and 5-to-32 versions with the addition of a single inverter.

SKU: D2027 - 74LS And 74HC Series IC

74hc147 IC in Pakistan

The 74HC/HCT147 are high-speed Si-gate CMOS devices and are pin compatible with low-power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT147 9-input priority encoders accept data from nine active LOW inputs (A0 to A8) and provide a binary representation on the four active LOW outputs (Y0 to Y3). A priority is assigned to each input so that when two or more inputs are simultaneously active, the input with the highest priority is represented on the output, with input line A8 having the highest priority. The devices provide the 10-line to 4-line priority encoding function by use of the implied decimal “zero”. The “zero” is encoded when all nine data inputs are HIGH, forcing all four outputs HIGH.

SKU: D2032 - 74LS And 74HC Series IC

74hc151 IC in Pakistan

74HC151 is 8 – Input Multiplexer 16 Pin IC. Data Selector/Multiplexer contains full on-chip decoding to select one-of-eight data sources as a result of a unique three binary code at select inputs. Two complementary outputs provide both inverting and non-inverting buffer operation. A Strobe input is provided which, when at a high level, disables all data inputs and forces Y output to low state and W output to a high state. Select input buffers incorporate internal overlap features to ensure that select input changes do not cause invalid output transients. Used for Boolean Function Generator.

SKU: D2031 - 74LS And 74HC Series IC

74HC157 Quad 2×1 Multiplexer MUX DIP IC SN74LS157N 74157 74-LS157 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74HC157 Quad 2×1 Multiplexer MUX DIP IC SN74LS157N 74157 74-LS157 in Pakistan

74HC157 is a high-speed multiplexer integrated circuit consisting of four 2-input digital multiplexers inside the chip. It is pin-compatible with Low-power Schottky TTL. It has two control inputs namely enable and select input. Additionally, it has two groups of registers. The selected input determines the register from which the data comes. Its operation is specified over a temperature range of -55 °C to 125 °C.

SKU: D2001