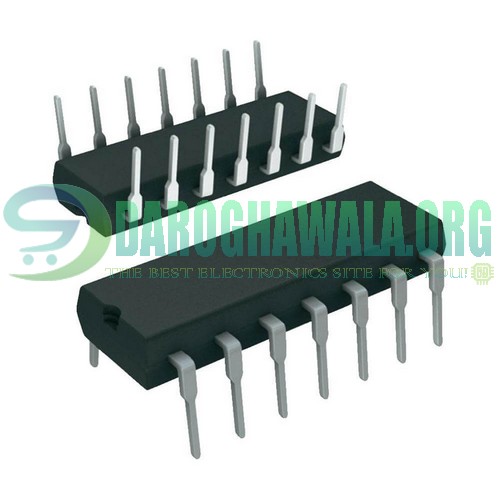

7475 74LS75 4-BIT BISTABLE LATCHES in Pakistan

7475 74LS75 4-BIT BISTABLE LATCHES in Pakistan

7475 74LS75 4-BIT BISTABLE LATCHES in Pakistan

Package Include:

- 1x 7475 74LS75 4-BIT BISTABLE LATCHES in Pakistan

Related products

- 74LS And 74HC Series IC

7448 BCD To 7 Segment Decoder Driver IC 74LS48 SN74LS48N 74HC48 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC7448 BCD To 7 Segment Decoder Driver IC 74LS48 SN74LS48N 74HC48 in Pakistan

0 out of 5(0)The 74LS48 features active-high outputs for driving lamp buffers or common-cathode LEDs. They have full ripple-blanking input/output controls and a lamp test input. Display patterns for BCD input count above 9 are unique symbols to authenticate input conditions. Their circuits incorporate automatic leading and/or trailing-edge zero-blanking control (RBI\ and RBO\). Lamp test (LT\) of these types may be performed at any time when the BI\/RBO\ node is at a high level. They contain an overriding blanking input (BI\), which can be used to control the lamp intensity by pulsing or to inhibit the outputs. Inputs and outputs are entirely compatible for use with TTL logic outputs.

SKU: D2010 - 74LS And 74HC Series IC

74LS76 DUAL JK FLIP-FLOP IC in Pakistan

0 out of 5(0)74LS76 comes with dual JK flip-flops. JK flip flops are widely used in daily electronics devices by many methods but the basic operation of the JK flip flop is to store a bit. JK flip flop allows it to store a bit and then allows it to use for further functions. in digital electronics circuits. JK flip flop is one of the popular flip flops due to its clock input, pre-set, and clear functionalities. The JK flip-flop changes its state under the clock pulse signal. The clock signal can be either a positive edge or a negative edge. The clock pulse gives multiple advantages to the flip-flop. 74LS76 also has provided a feature to neglect or prevent invalid outputs.

SKU: D2025 - 74LS And 74HC Series IC

74HC165 Parallel To Serial 8 Bit Shift Register IC in Pakistan

0 out of 5(0)The 74HC165 is a high-speed Si-gate CMOS device and is pin-compatible with low-power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC165 are 8-bit parallel-load or serial-in shift registers with complementary serial outputs (Q7 and Q7) available from the last stage. When the parallel load (PL) input is LOW, parallel data from the D0 to D7 inputs are loaded into the register asynchronously. When PL is HIGH, data enters the register serially at the Ds input and shifts one place to the right (Q0 –> Q1 –> Q2, etc.) with each positive-going clock transition. This feature allows parallel-to-serial converter expansion by tying the Q7 output to the DS input of the succeeding stage. The clock input is a gated-OR structure that allows one input to be used as an active LOW clock enable (CE) input. The pin assignment for the CP and CE inputs is arbitrary and can be reversed for layout convenience. The LOW-to-HIGH transition of input CE should only take place while CP is HIGH for predictable operation. Either the CP or the CE should be HIGH before the LOW-to-HIGH transition of PL to prevent shifting the data when PL is activated.

SKU: D2016 - 74LS And 74HC Series IC

74LS160 74160 74HC160 4-Bit Synchronous Decade Counter in Pakistan

0 out of 5(0)The 74LS160 IC package, consisting of 16 pins, contains a single 4 bit synchronous counter circuit which can be wired for decade counting mod, without external logic chips. By wiring more than one 74LS160 together (cascading), it is possible to make higher count lengths (powers of ten). For example, two 74LS160s cascaded together would yield a counter capable of decimally counting the range 00 – 99.

SKU: D2026

Reviews

There are no reviews yet