- Raspberry Pi & Accessories

- Raspberry Pi Kits

- Raspberry Pi Board

- Raspberry Pi Case

- Raspberry Pi Came

- Raspberry Pi Accessories

7426 Quad Two input NAND, High voltage in Pakistan

7426 Quad Two input NAND, High voltage in Pakistan

7426 Quad Two input NAND, High voltage in Pakistan

Packing list:

- 1x 7426 Quad Two input NAND, High voltage

Related products

- 74LS And 74HC Series IC

74LS189 64 Bit RAM with 3 State Output IC 74189 74HC189 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74LS189 64 Bit RAM with 3 State Output IC 74189 74HC189 in Pakistan

0 out of 5(0)The 74LS189 is a high-speed 64-bit RAM organized as a 16-word by the 4-bit array. Address inputs are buffered to minimize loading and are fully decoded on-chip. The outputs are 3-state and are in the high impedance state whenever the Chip Select (CS) input is HIGH. The outputs are active only in the read mode and the output data is the complement of the stored data.

SKU: D2011 - 74LS And 74HC Series IC

74LS148 3-Bit Priority Encoder IC (74148 IC) DIP-16 in Pakistan

0 out of 5(0)74LS Series ICs are High-Speed Logic gates, ideally a little faster than the 74HC series but more power consumption is required. They are implemented with a Low-Power Schottky diode technology to achieve high switching speed. 74LS148 is one of the 74LS series IC. 74LS148 ICs contain an 8 to 3-Bit priority encoder that converts 8 Data Lines to 3-Line binary. Cascading circuitry (enable input EI and enable output EO) has been provided to allow octal expansion without the need for external circuitry.

SKU: D2024 - 74LS And 74HC Series IC

SMD 74HC595 74HC595D SOP16 Patch 8 Bit Serial Shift Register in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series ICSMD 74HC595 74HC595D SOP16 Patch 8 Bit Serial Shift Register in Pakistan

0 out of 5(0)74HC595 8-bit Serial-to-Parallel Shift Register is a high-speed shift register that utilizes advanced silicon-gate CMOS technology. This device possesses the high noise immunity and low power consumption of standard CMOS integrated circuits, as well as the ability to drive 15 LS-TTL loads.

This device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. The storage register has 8 3-STATE outputs. Separate clocks are provided for both the shift register and the storage register.

The shift register has direct-overriding clear, serial input, and serial output (standard) pins for cascading. Both the shift register and storage register use positive-edge triggered clocks. If both clocks are connected together, the shift register state will always be one clock pulse ahead of the storage register.

The 74HC logic family is speed, function, and pin-out compatible with the standard 74LS logic family. All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.

SKU: D2013 - 74LS And 74HC Series IC

74LS32 74-LS32 74HC32 7432 Quad 2 Input OR Gate DIP IC SN74CH32N in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74LS32 74-LS32 74HC32 7432 Quad 2 Input OR Gate DIP IC SN74CH32N in Pakistan

0 out of 5(0)This device contains four independent gates each of which performs the logic OR function. The 74LS32 is a 14-Pin Quad 2-Input OR Gate IC. The 74LS32 provides four independent 2-input OR gates with standard push-pull outputs. Featured by Sharvi Electronics The device is designed for operation with a power supply range of 2.0V to 6.0V. Inputs include clamp diodes. This enables the use of current-limiting resistors to interface inputs to voltages in excess of VCC.

SKU: D2000 - 74LS And 74HC Series IC

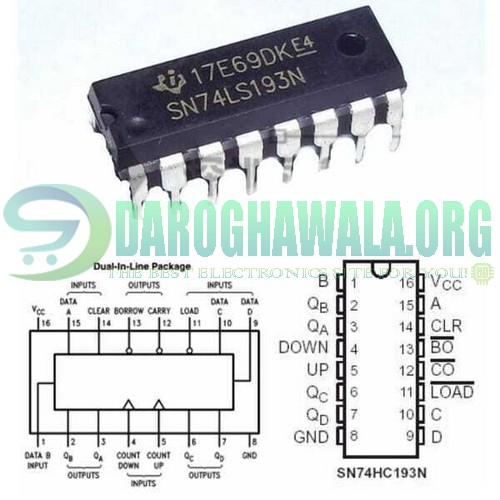

74193 Synchronous 4 Bit Binary Counter DIP IC SN74LS193N 74HC193 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74193 Synchronous 4 Bit Binary Counter DIP IC SN74LS193N 74HC193 in Pakistan

0 out of 5(0)This circuit is a synchronous up/down 4-bit binary counter. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change together when so instructed by the steering logic. This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple clock) counters. The outputs of the four master-slave flip-flops are triggered by a low-to-high level transition of either count (clock) input. The direction of counting is determined by which count input is pulsed while the other count input is held high. The counter is fully programmable; that is, each output may be preset to either level by entering the desired data at the inputs while the load input is low. The output will change independently of the count pulses.

SKU: D2015

Reviews

There are no reviews yet