- Raspberry Pi & Accessories

- Raspberry Pi Kits

- Raspberry Pi Board

- Raspberry Pi Case

- Raspberry Pi Came

- Raspberry Pi Accessories

Related products

- 74LS And 74HC Series IC

74HC157 Quad 2×1 Multiplexer MUX DIP IC SN74LS157N 74157 74-LS157 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74HC157 Quad 2×1 Multiplexer MUX DIP IC SN74LS157N 74157 74-LS157 in Pakistan

0 out of 5(0)74HC157 is a high-speed multiplexer integrated circuit consisting of four 2-input digital multiplexers inside the chip. It is pin-compatible with Low-power Schottky TTL. It has two control inputs namely enable and select input. Additionally, it has two groups of registers. The selected input determines the register from which the data comes. Its operation is specified over a temperature range of -55 °C to 125 °C.

SKU: D2001 - 74LS And 74HC Series IC

7404 74LS04 74HC04 Hex Inverter IC in Pakistan

0 out of 5(0)The 7404 is a triple-buffered inverter. It has high noise immunity and the ability to drive 10 LS-TTL loads. The 74HC logic family is functionally as well as pin-out compatible with the standard 74LS logic family. All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.

SKU: D2004 - 74LS And 74HC Series IC

74151 ic in Pakistan

0 out of 5(0)This Data Selector/Multiplexer contains full on-chip decoding to select one-of-eight data sources as a result of a unique three-bit binary code at the Select inputs. Two complementary outputs provide both inverting and non-inverting buffer operation. A Strobe input is provided which, when at the high level, disables all data inputs and forces the Y output to the low state and the W output to the high state. The Select input buffers incorporate internal overlap features to ensure that select input changes do not cause invalid output transients. RoboticsBD

SKU: D2022 - 74LS And 74HC Series IC

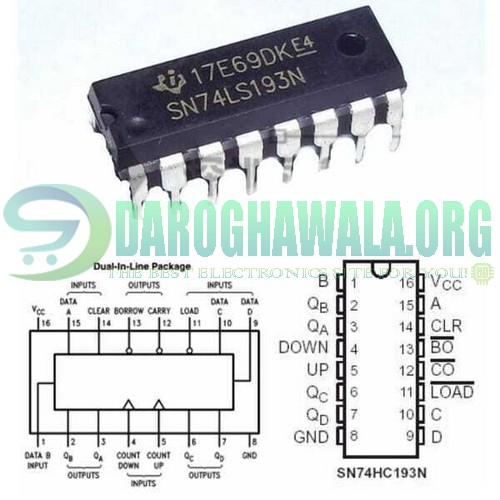

74193 Synchronous 4 Bit Binary Counter DIP IC SN74LS193N 74HC193 in Pakistan

Quick View 74LS And 74HC Series IC

74LS And 74HC Series IC74193 Synchronous 4 Bit Binary Counter DIP IC SN74LS193N 74HC193 in Pakistan

0 out of 5(0)This circuit is a synchronous up/down 4-bit binary counter. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change together when so instructed by the steering logic. This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple clock) counters. The outputs of the four master-slave flip-flops are triggered by a low-to-high level transition of either count (clock) input. The direction of counting is determined by which count input is pulsed while the other count input is held high. The counter is fully programmable; that is, each output may be preset to either level by entering the desired data at the inputs while the load input is low. The output will change independently of the count pulses.

SKU: D2015

Reviews

There are no reviews yet